Intelは3月5日、6日(米国時間)の2日間に渡り、同社最大の工場を擁する米オレゴン州ヒルズボロにおいて、次世代データセンター向けポートフォリオに関する報道陣向けワークショップを開催しました。ワークショップ全体を通して語られたテーマは「データセントリックな世界(Data-Centric World)」で、具体的には

- クラウドコンピューティングへのシフト

- AIおよびアナリティクス関連のワークロードの急増

- (5GやNFVなど)ネットワークおよびエッジコンピューティングの進化

という3つの大きなトレンドに沿って、データセンター向けポートフォリオを拡充していく姿勢を示しています。

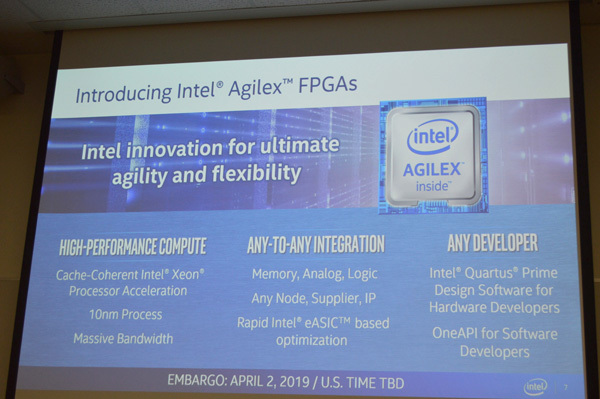

数多くの新製品や新戦略が語られたワークショップにあって、ひときわ注目されていたトピックがFPFA(Field Programmable Gate Array)製品群の「Agilex」ファミリでした。Intelは2015年、Xilinxと並ぶFPGAのリーディングカンパニーであったAlteraを買収し、業界に大きな衝撃を与えましたが、その後の技術統合やロードマップ刷新が後手後手に回ってしまい、とくに主力となる10nmプロセスの開発において競合のXilinxに大きく水を開けられた状態にありました。3年もの時間をかけ、ヒルズボロというIntelの本拠地で発表されたAltera後継のFPGA「Agilex」はどんなアーキテクチャなのでしょうか。本稿では現地での取材をもとに、その概要を紹介します。

3年の月日が費やされたAlteraの資産を受け継ぐFPGA「Intel Agilex」

さまざまな技術の融合がイノベーションを呼び起こす

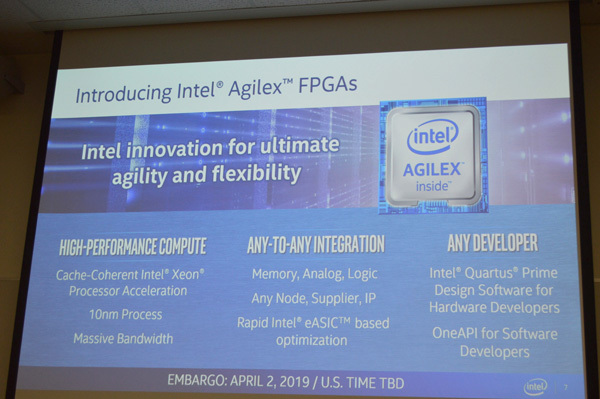

「Agilexはデータセントリックワールドへとあらゆる企業をいざない、ビジネスを"アクセラレート"する存在。イノベーションを呼び起こす究極のアクセラレータとなるFPGAを目指した」―Intel プログラマブルソリューショングループ CTOオフィス シニアマネージャ ホセ・アルバレス(Jose Alvalez)氏はワークショップの冒頭、Agilexの開発目的についてこう語っています。

ホセ・アルバレス氏

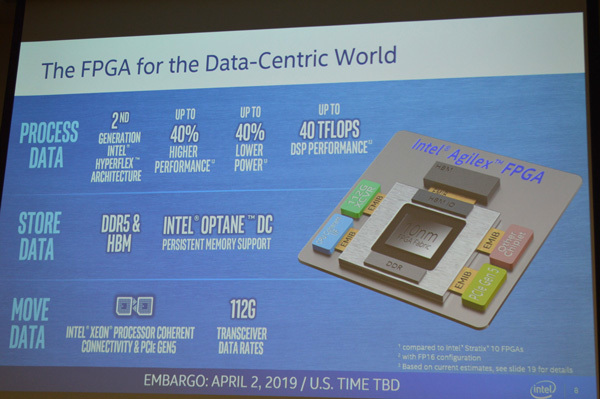

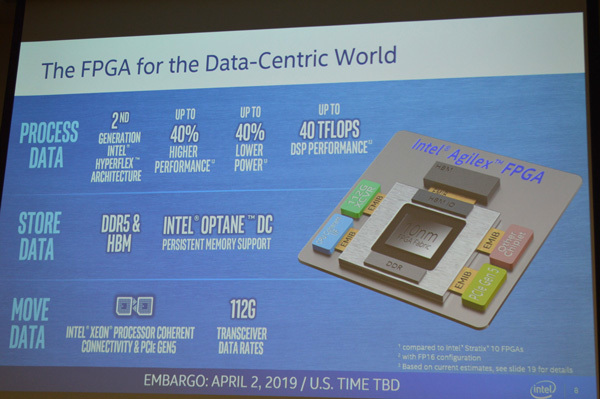

Intelにはすでに「Intel Stratix 10 FPGA」というFPGAファミリが存在しており、「Intel Hyperflex」アーキテクチャをベースにしていますが、AgilexのFPGAファブリックについては「2nd Gen Intel Hyperflex Architecture」という説明がありました。つまり、基本的にはStratix 10のファブリックをコアにしつつ、Alteraの技術を統合することで、AgilexはStratix 10よりも1世代先を行くFPGAとして位置づけられることになります。

アルバレス氏はAgilexをStartix 10と比較して「パフォーマンスは40%アップ、省電力も40%アップ、さらにDSPパフォーマンスは40TFLOPSまで向上した」と語っており、大幅な高速化が図られていることが伺えます。また、外部メモリとして次世代メモリのDDR5とHBMをサポートするほか、Intelが開発する最新のパーシステントメモリ「Intel Optane DC Persitent Memory」をサポートし、データセンターのモダナイズに最新の技術でもって対応している点も特徴です。

「データセントリックワールド」に最適化された設計をめざしたというAgilex。パフォーマンスや省電力も大幅に向上し、3DパッケージングやCPU⇔FPGA間のキャッシュコヒーレントなインターコネクトなど業界初となる技術を数多く実装

Agilexにはこのほかにも"イノベーションのアクセラレータ"として機能するべく、業界初(あるいはIntel初)となる画期的な最先端技術が実装されています。以下にそのメインとなる技術を挙げておきます。

10nmプロセス

Intel既存のFPGAファミリであるStratix 10は14nmプロセスにとどまっており、より微細化した10nmプロセスの実装は、微細化で先を行く競合のXilinxの状況を考えても、どうしても実現しなければならないゴールでした。今回の発表に至ったことにより、ようやく10nmプロセス量産のめどが立ったことがうかがえます。

3Dパッケージング

Agilexでは「EMIB(Embedded Multi-Die Interconnect Bridge)」というIntelが開発した高密度パッケージング技術が使われており、FPGAファブリックとは別に、各チップレット(トランシーバやカスタムI/O、カスタムタイルなど)が基板上に配置されます。チップレットはカスタマイズ可能で、アルバレス氏は「"Any-to-Any"を実現するヘテロジニアスなチップレットベースのパッケージング」であることを強調しています。また、より柔軟なカスタマイズを実現するため「Intel eASIC」(Intelが2018年7月に買収したストラクチャードASICベンダeASICの技術)チップレットも搭載可能となっています。

EMIBは正確には2.5次元のパッケージング技術であり、Intelが2018年12月に発表したロジックどうし(CPUとGPUなど)のヘテロジニアスなスタッキングを可能にする3次元パッケージング技術「Foveros」とは異なりますが、あえて今回、Agilexを「ヘテロジニアスな3Dパッケージング技術をベースにするFPGA」(アルバレス氏)としているのは、将来的にFoverosを含む本格的な3Dパッケージング技術に対応させる予定を見込んでのことだといえます。

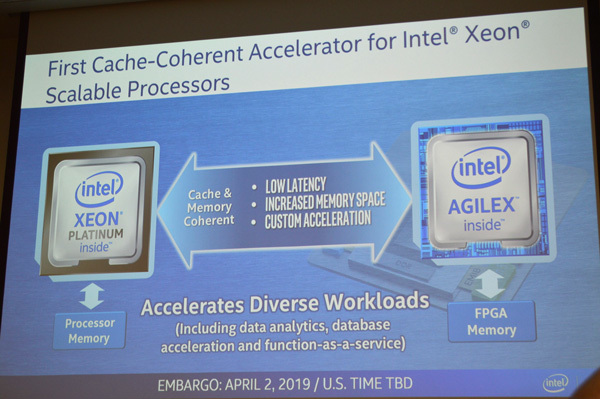

CXL(Compute Express Link)

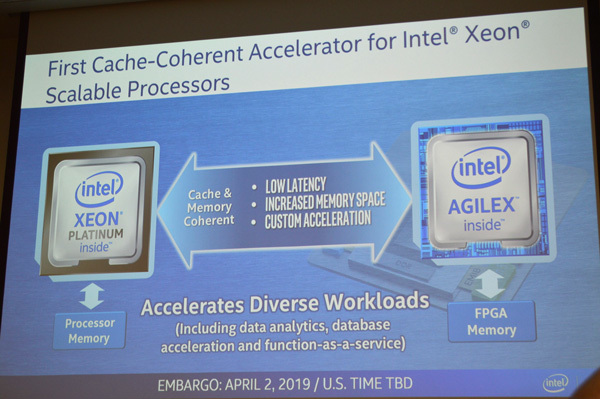

Agilexにおいて、もっとも革新的といえる技術がこのCXLかもしれません。CXLはFPGAとデータセンター向け製品である「Intel Xeon Scalable」プロセッサとの間で、キャッシュコヒーレントなインターコネクトを実現するアーキテクチャで、プロセッサとデバイス(FPGA)の間でメモリおよびキャッシュの一貫性を維持することが可能になります。これにより、低レイテンシなデータアクセスやリソース共有によるメモリ空間の増加といったメリットがもたらされ、「データアナリティクスや高速なデータベースアクセス、FaaS/サーバレスといった需要が急増しているモダンなワークロードに対し、高速なアクセスが可能になる」(アルバレス氏)ことが期待されます。

なお、筆者がヒルズボロで説明を受けた時点(3/5)では、まだ「CXL」という名称は明らかになっていませんでしたが、Intelは3月11日(米国時間)に行った別のイベントにおいて、本技術をPCIe Gen5上で実装される新規格として発表しています。つまりAgilexとXeon ScalableプロセッサはPCIe Gen5ベースでCLXを具現化する最初のFPGAとCPUのペアとなるわけで、FPGAだけでなくCPU側でのPCI Gen5対応が急がれます。

Agilexに搭載されたもっとも革新的な技術といえるのが、XeonプロセッサとFPGAの間でメモリとキャッシュの一貫性を維持するインターコネクト技術。低レイテンシやリソース共有など多くのベネフィットが提供される

チップレットとして提供される112Gbpsのトランシーバ

アルバレス氏は「AgilexはFPGAトランシーバにおいても大きなイノベーションを実現した」と強調していましたが、10nmプロセスと同様、トランシーバの高速化もAgilexにおいてかなり苦労した部分だったようです。Agilexでは最大で112GbpsおよびPCIe Gen6のトランシーバを搭載しています。

400Gなどデータセンターにおける高帯域へのニーズが急激に増えていることから、FPGA内蔵トランシーバの高速化は避けて通れない課題であり、Intelは10nmプロセスに特化した112G PAM-4トランシーバの開発を進めてきましたが、ようやくAgilexで実現したことになります。前述したように、この新しいトランシーバがチップレットとして別に製造され、その後、EMIBでもってAgilexとしてパッケージングすることで、柔軟性を担保している点も大きな特徴のひとつです。

PCIe Gen5対応

後述しますが、Agilexファミリには3つのシリーズがあり、このうちミドルエンドとハイエンドのシリーズでは現行で最新世代の高速バスインタフェース規格であるPCIe Gen5対応となっています。CXLやトランシーバでPCIe Gen5をサポートしていることからもわかるように、後発だからこそ、ハイパフォーマンスなFPGAに徹底的にこだわってきた姿勢がうかがえます。

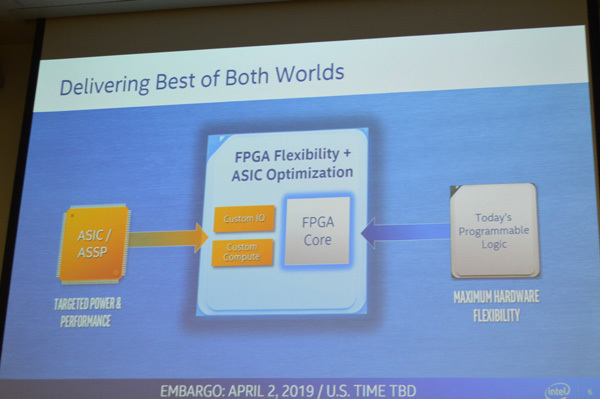

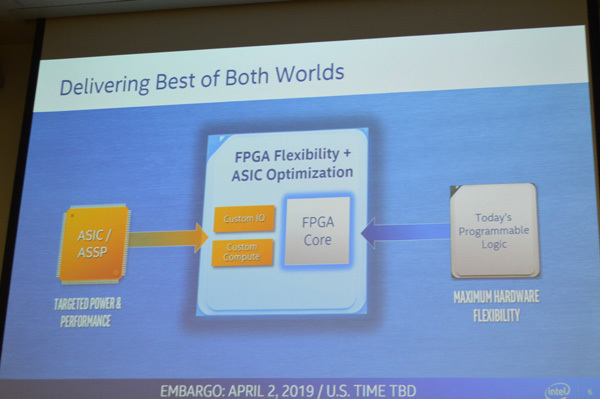

Intel eASICの統合

パッケージングの項で触れましたが、AgilexではIntelが買収したeASICの技術がチップレットとして搭載可能となっています。Alteraと同様に、IntelがeASICを買収したニュースは多くの業界関係者を驚かせましたが、技術的にFPGAとASICの中間に位置するともいえるeASICは、カスマイズの柔軟性と一貫性をより高める存在となることは間違いなく、Intelにとって今後のFPGA市場における大きな差別化要因となる可能性があります。

特定の用途に最適化されたASICとプログラマブルなFPGA、その両方の良さを1つのチップで実現したのが「Agilex」

OneAPI

Agilexは開発者に対しても「Any Developer」のポリシーのもと、多くのツールやドキュメントを公開していくことを約束しています。その代表的な取り組みが「OneAPI」と呼ばれるソフトウェア開発者向けのリソース提供で、「より多くの開発者にとって有益になるよう、さまざまなプログラミング環境をシングルソースでサポートしていく」と語っていますが、具体的には標準的なAPIや、パフォーマンス解析ツールの「Intel VTune Amplifier」、アプリケーションパフォーマンス最適化ツール「Intel Advisor」など、FPGAと関連性の深いソフトウェアやライブラリをワンストップでサポートすることから始めていくようです。

また、ハードウェア開発者向けのサポートとしては、すでにIntelが提供しているプログラム「Quartus Prime」を継続していくことが明らかになっています。

Intel Optane DC Persistent Memory

前述しましたが、Agilexは「初めてパーシステントメモリを実装するFPGA」(アルバレス氏)であり、こちらも今回のワークショップで説明が行われた「Intel Optane DC Persistent Memory」をサポートします。Optane DCに関しては2018年ごろから「データセンターのあり方を変えるパーシステントメモリ技術」として話題になっていましたが、データセンターにおけるホットデータ(アクセス数の多いデータ)をできるだけ低コスト&省電力で扱うためにIntelが開発した「メモリとストレージの両方の属性を兼ね備えたアーキテクチャ」(Intel)であり、FPGAが本格的にこれをサポートするようになれば、AI/データアナリティクスといったワークロード処理が劇的に向上することが期待されます。

「Agilex」の名に込められた開発の道しるべ

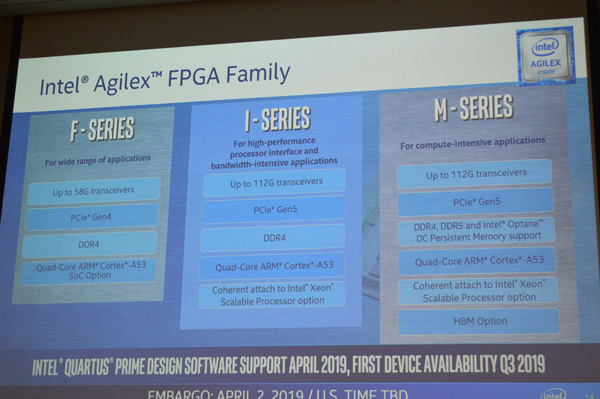

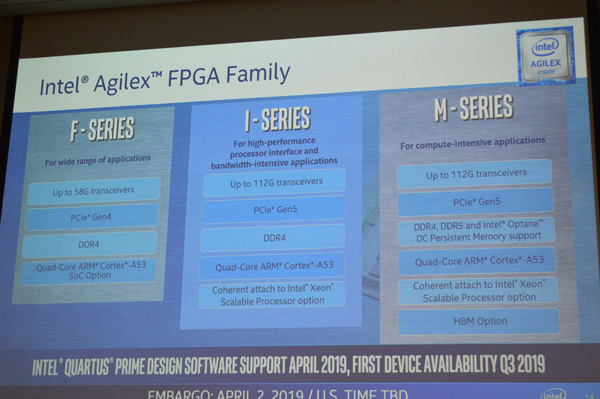

さまざまな最新技術が搭載されたAgilexファミリですが、Intelは現在、3つのシリーズの提供を予定しています。

- Fシリーズ(ローエンド)

- 最大通信速度58Gbpsのトランシーバ、PCIe Gen4、DDR4、オプションでクアッドコアARM Cortex A-53 SoC

- Iシリーズ(ミドルエンド)

- 最大通信速度112Gbpsのトランシーバ、PCIe Gen5、DDR4、クアッドコアARM Cortex A-53、オプションでCXL

- Mシリーズ(ハイエンド)

- 最大通信速度112Gbpsのトランシーバ、PCIe Gen5、DDR4/DDR5/Intel Optane DC Persistent Memory、クアッドコアARM Cortex A-53、オプションでCXL、オプションでHBM

CXLやパーシステントメモリ、DDR5、HBMなどの最新技術はIシリーズ以上での提供となります。

Agilexファミリには3つのラインナップが用意される。CXLなどの最新技術が実装されるのはミドルエンドのIシリースとMシリーズでHPCや通信業界などでの需要が見込まれている

アルバレス氏はワークショップにおいて「ASICの最適化技術とFPGAのフレキシビリティ、Agilexその2つの良さを最大限に活かせるアーキテクチャをめざした」と語っていましたが、FPGA市場で図らずしも後発の立場となったIntelがAgilexでもっとも注力したことは「フレキシビリティ(柔軟性)」ではないかという印象を個人的にもちました。

ここまで紹介したように、Agilexには数多くの最新技術が実装されていますが、3Dパッケージングや112Gトランシーバのチップレット提供にも見られるように、高速性や大容量化を目指しながらも、仕様を固めすぎずないことに大きな労力を払っています。「Agilexではエコシステムを構築しやすいように、多くの技術と連携できることを意識した」とアルバレス氏は語っており、競合との差別化以上に、顧客や市場のニーズに柔軟に対応できるアーキテクチャにこだわった点を強調しています。

ここ数年、Intelのビジネスは決して好調とは言い難く、FPGAに関してもAWSやAlibabaとの連携や大企業での採用増加など良いニュースが続くXilinxとは対象的に、3年もの間、Altera後継プロダクトを発表できない状況にありました。そしてようやく、ヒルズボロというIntelにとってもっとも重要な拠点で発表されたAgilexには、"Agility"と"Flexibility"という2つの意味が込められています。迅速であること、柔軟であること、この2つのキーワードはFPGAに限らず、これからのIntelの製品開発においてつねに求められる指針になるように思えます。