DSSD D5は、2016年2月末にEMC Worldで発表された、いわゆるAll Flashストレージシステムです[1] 。多数のサーバを同じラックに詰めて1つのシステムとして利用する、ラックスケールなアプライアンスであり、かつてない超高性能を狙ったものです。

筆者は2016年の3月にDSSD社を訪問して、その開発に深く関わってきたAndy Bechtolsheim氏にインタビューする機会を得て、DSSDの技術やその起業にまつわるストーリーなどを聞くことができました。

取材当日のAndy

今回の取材では、D5がその高い性能を実現している機構を理解することに集中してAndyに質問しました。筆者は以前にも一度Andyを取材したことがありますが[2] 、彼は技術的に意味のある質問には常に真っ直ぐ丁寧に説明してくれます。1時間少しの取材によって、筆者はDSSDがシステム全体のアーキテクチャと多数のエンジニアリングの積み重ねによって総合的に高い性能を実現していることを理解しました。

以下に取材で交わされた会話を元に、そのあたりの説明を試みます。

(すべての記述は筆者の解釈・理解に基づいたものです。もし錯誤があったとしてもご容赦ください) 。

DSSD D5

D5の開発ははじめ、そのためにスタートアップしたDSSD社によって行われていました。しかし2014年の5月にEMC社がDSSD社を買収したため、現在はEMCの製品として販売されています。

DSSDのエントランス

DSSDの起業は2010年の夏ですが、設立時からAndy Bechtolsheim氏が関わっていたことから注目され[3] 、また長いステルスモードの間、何を開発しているのかほとんど表に出てこなかったために、長く「謎の起業」としてIT業界人から認知されていました[4] 。

発表されたD5は、5Uサイズの筐体にNVMeベースの専用Flash Moduleを最大144Tバイト収め(データ格納量は100Tバイト) 、最大48台のサーバを接続できる、ラックスケールの超高性能ストレージシステムでした。なんと10M IOPS、100GB/secスループットを遅延100μsecで提供するとあります。従来的なシステムの10倍高速である、と謳われています。

ラボで見せてもらったD5。球付きの小型ラックにセットされていたのでデモ用か。上下に4台のDELLサーバを配置

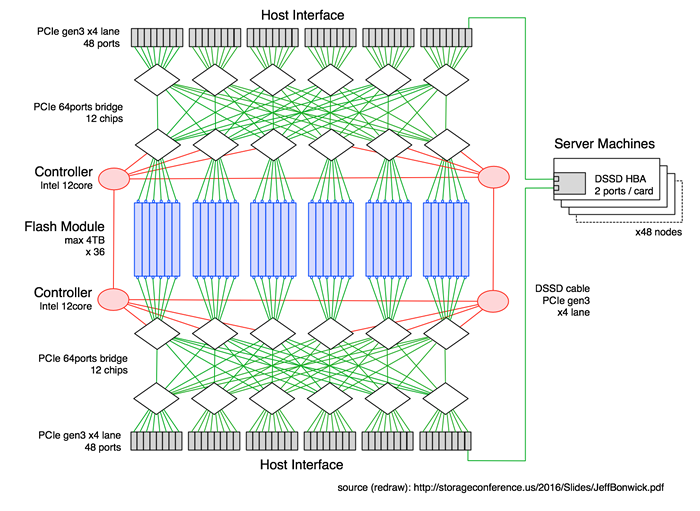

36枚の専用Flash Moduleと48台のサーバは大規模なPCIe Fabricを用いて相互接続されます。またシステム全体の制御のためにIntel CPUを2つ積んだコントローラボードが2枚入っています(図1 ) 。

図からわかるように、Fabricとコントローラボードを1つの組としてそれぞれ独立に構成することで冗長性を高めています。サーバマシンはDSSD専用のHBA(Host Bus Adapter)を2枚持ち、そこからこの2つのFabricの両方に接続します。最大4Tバイトの容量があるFlash Muduleもまたインターフェースを2つ持ち、この2つのFabricの両方に接続しています。サーバから両手を回して、2つのFabricを介してFlash Moduleを抱え込む格好ですね。

図1 D5システム構成図“ Scalable High Performance Flash Systems” 、Jeff Bonwick Co-founder and CTO, DSSD / EMC, MSST 2016と取材時の情報からリドロー。筆者の取材から2ヵ月後にDSSDのCTOによって行われた発表 です

D5ではこれらすべての構成要素をPCIeで接続しています。つまり、サーバからFlash Moduleまでのすべての経路をPCIeで統一して究極の低遅延アクセスを手に入れるために設計されたシステムであり、それを実現するために設計努力を集中させています。

まず、PCIeは現代のサーバ向けCPUにとって最速のI/Oインターフェースであることに注意が必要です。Intelをはじめ、多くのプロセッサはPCIeインターフェースをCPUのシリコンダイ上に実装しています。つまりサーバCPUから直接出ているPCIeインターフェースからFlash Moduleまでのすべての経路をPCIeで統一することは、一切のプロトコル変換を取り除けることを意味します。

もし、I/O機器を何か別のインターフェース、たとえばSASを用いて接続にすると、常にPCIe―SASといったプロトコル変換(データの変換)が必要となり、そのぶんアクセス遅延が生じます。

NVMeやioDriveのようなPCIe直結のSSDはこの点を追求したものです。ただ、PCIeは一般にホストシステム内のスロットにデバイスを挿す形で利用されており、ケーブルを介して筐体外で接続する製品はとても少数です。

実際のところPCIeは上位層ではPCIバス互換ですが、内部的には階層化された(トランザクション層やデータリンク層などが普通にある)パケット構造とプロトコルで構成された、ほぼネットワークシステムと思って良いものです。そのままネットワークシステムとして使えるような構造であるはずなのに、ちょっともったいないと個人的には思っています[5] 。

つまり、複数ホストからケーブルを介して共有ストレージをPCIeでアクセスするためには、その部分の技術開発が必要です。そしてできあがったシステム規模の大きさを見ると、投入したであろう開発努力の量に驚きます。各要素部品の構成を見るとFlash ModuleにはPCIe gen3を4レーン使ったポートが2つあり、これが36枚分の合計で72ポート。サーバのHBAも同じくPCIe gen3の4レーンインターフェースが2ポートで48台の96ポート。これらをPLX(現 Avago)製のPCIe gen3 64レーン(16ポート)のブリッジチップを12個使ってフルメッシュ接続したファブリックボード2枚で相互接続するのです。でかい、と言うほかありません。

あまりのゴージャスさに「すごいFabricですねえ」と筆者が言うと、Andyは「実のところ過去最大のPCIe fabricだと思いますよ。12もチップを使っていて、これを冗長性のために2つ、つまり24個使っているのですから。」と笑っていました。

[3] AndyはSun Microsystems社の共同創業者であり、他にも多くの会社を起業し成功させたシリアル・アントレプレナーとして、あるいはGoogleをはじめとした複数企業のエンジェル・インベスターとして有名で、その挙動は常に多くの人の注目を集めています。

コントローラによるアービトレーションとRDMA

PCIe Fabricの物理的な構成がわかったところで、次に興味が湧くのはそのアクセス方式です。

D5ではサーバとFlash Module間のデータ転送はPCIeのRDMAを用いて行われます。つまり、Flash Moduleはすべてサーバのメモリ空間に割り付けられています。ただし、CPUのread/write命令がそのままFlash Moduleをアクセスすることはできず、まず、I/Oのイニシエートが必要です。D5におけるイニシエートとは実質、コントローラによるFabricのアービトレーション(調停)です。D5には強力なIntel CPU[6] と大量のメモリを積んだコントローラが搭載されており、FabricにPCIeで接続されています。

サーバがFlash Moduleにアクセスするときは、つねにこのコントローラのアービトレーション(調停)を受けて経路を確保してデータを高速に送り込みます。これでFabcric上でのアクセス衝突やブロッキングが一切生じない、最高速度でのRDMAデータ転送を実現します。具体的な手順は以下のようなものです。

サーバがコントローラに経路の割り当てを依頼

コントローラが経路を確保してサーバにGOを出す

サーバがデータを送り出す

もしエラーがあればコントローラからサーバに通知が行われる

つまり、データの転送そのものにはコントローラのCPUやメモリは一切使用せず、point to pointに接続されたサーバとFlash Moduleが直接やりとりします。Andyは「我々はDMAの帯域を邪魔するものをすべて取り除く」と言い、このコントローラによるアービトレーションを用いたアクセスの効率の良さを強調していました。

Andyはまた取材のあいだ、何度もIntelの3D XPoint Memoryや3D NAND Flashなど次世代の不揮発性メモリの予想される性能数値を挙げ、その領域でもこのコントロールプレーンが十分機能することを強調していました。

Andy: 素子レベルではサブマイクロ秒で動作するようなもの(次世代メモリ技術)が出てくるでしょう。デバイスとしては 20μ秒あたりで動作するようになるでしょう(D5は100μ秒) 。

筆者: 次世代のメモリシステムが登場したら、アプリケーションはより短いレイテンシを要求するでしょうね。

Andy: ええ。

筆者: そうした場合に、次のバージョンのD5で高いパフォーマンスを出すために最も困難な点は何でしょう?

Andy: それは簡単です。というのも我々はすでにそうした未来のために(現行のD5を)設計したから。我々のアーキテクチャはより低い遅延を提供するでしょう。伝統的なSAS SSDなどでは困難なことです。なぜなら、SCSIには多くのオーバーヘッドがあって、新しいテクノロジを入れてもそれら他のオーバーヘッドのために良い性能が出ないからです。高性能のためには(D5同様に)NVMeを使わなければならないのです。

つまり、次世代ストレージではNVMeが必要になるが、DSSDはその性能を十分に活かし、大規模かつ低遅延でアクセスするのに十分な設計をこのD5でもうやってしまった、というわけです。

Flood API

DSSDによると従来的なFlash共有ストレージの典型的なアクセス遅延は500μ秒となっています。D5は、先に述べた工夫によって(サーバ内部のPCIeスロット直結ではない)共有ストレージでありながらこのアクセス遅延を100μ秒にまで短縮することに成功しました。

しかし、その500μ秒にはアプリケーションがストレージにアクセスするまでの間に存在する分厚いソフトウェアスタックによるオーバーヘッドが多く含まれています。ライブラリ呼び出し、システムコールの発生、ファイルシステム、デバイスドライバを経てようやくHBA(Host Bus Adapter)に命令が送り込まれる、といったプロセスの中にです。

D5ではこれをバイパスするFloodと呼ばれるソフトウェアスタックを用意し、このオーバーヘッドを削減しています。もう少し踏み込んで内部構造について聞いてみました。

Andy: 我々はソフトウェアをもっと掘り下げました。つまり我々は高速化のためにライブラリレベルでDMA転送を起こすのです。それでPCIe Fabricがデータを100μ秒でデリバリできるようになりました。

筆者: その作業はすべてユーザランドで実行されるのですか?[7]

Andy: いや、( それだけでなく)もっと高速にやります。( 内部的には)シングルスレッドになっています。つまりシリアライズされるのです。各アプリケーション、各プロセッサコアがそれぞれのキューをとって並列に扱います。そこですべてのI/Oリクエストは1つのキューに入り、並列に処理されます。

我々はエミュレーションによって 10,000 キューが必要なことを認識しました。つまりこれ(そうしたリクエスト群)をスケジューリングして、もし物理的なダイが利用可能な状態なら、サーバにそれをやらせてしまう(書き込みをDMAで実施する)ことができる、ということです。

ここで、もし2つのスレッドが1つのダイ[8] を上書きしようとしていた場合、早い者勝ちでシリアライズされます。しかし、18,000ダイが衝突を起こすことはほとんどありません。40サーバで16コアだった場合、同じダイになる可能性はとても低いです。

つまりほとんどの場合、あなたは100μ秒のパフォーマンスを得ます。何しろとても多くのパラレルなチップがあるのでね。これでどのすべてのコアも1GB/sec以上の速度で読み書きすることができますよ(笑)

これは、Intel CPUが本来的に持っている、各コアがマルチスレッドのI/Oを持つことをunableにできる機能を利用しているとのことです。CPU資源の使い方としては「高く付く」けれど「最終的な収支には見合う」とAndyは言います。つまり、これでシステム全体としては「ロックがなく、ボトルネックのない、すべてパラレルで、マルチスレッドのI/Oとなる」というわけです。

ところで内部的には、とくにハードウェアレベルではすべてのアクセスはRDMAですが、その上のソフトウェアレベルではロックも、ファイルもサポートしています。ただ、DSSDのネイティブなインターフェースであるFlood APIはオブジェクトFlood APIはオブジェクトストレージ、意味的にはKVS(Key Value Store)を指向しています。つまりロックやファイルはKVSをlookupする形で実装しています。このFlood APIを使うためにはユーザがソフトウェアをカスタマイズする必要がありますが、その代わりD5本来の、ネイティブなI/Oパフォーマンスが得られます。

また、DSSDはこれを利用したHadoopプラグインを用意しています。たとえば、Clouderaは彼らのHadoopディストリビューションであるCDHの管理ツールであるCloudera ManagerにDSSDをインテグレートしています*[9] 。これを利用する場合はアプリケーションの変更は不要です。

(後編に続く)