2019年11月、スパコン(スーパーコンピュータ)のトップカンファレンスであるSC19で、小形のAI専用スパコンがデビューをはたしました。「CS-1」と名付けられたそのマシンは、ウェハースケール、つまり30cmシリコンウェハーを一枚まるごと使った巨大なCPUをもち、その広大な領域に埋め込まれた40万ものコアに、ターゲットのニューラル・ネットワークをそっくり全部マッピングして並列動作させます。

このあまりにもシンプルで、かつ壮大なアイデアをストレートに実現したのはCerebras Systemsというスタートアップ・カンパニーです。

筆者はいくつものスタートアップ、とくにハードウェア・システムを開発する企業を見てきました。Cerebrasについても二年ほど前から何度か訪問して開発状況などを見てきましたが、これほど野心的なスタートアップは滅多にありません。

このCerebrasの技術についてはすでに多くの記事が、それも私の尊敬する方々によって出されています[1]。そこで本稿では、その技術ではなく起業の経緯などに焦点を当てた、つまりこのモンスターマシンを生んだ企業のスタートアップストーリーをお届けします。

CS-1

繰り返しになりますが、控えめに言ってもCS-1はとてつもないモンスターです。本記事はCerebrasの技術についてはあまり書かず、スタートアップストーリーや彼らの大きなビジョンを伝えることが目的なのですが、さりとて何も技術に関する情報がないと各エピソードの重みがわかりません。

そこでまずはじめに、簡単にCS-1のおおまかな設計について解説します。以下のCerebrasの各Blogがとても良くできているので、それを適宜引用して説明します。

WSE - Wafer Scale Engine

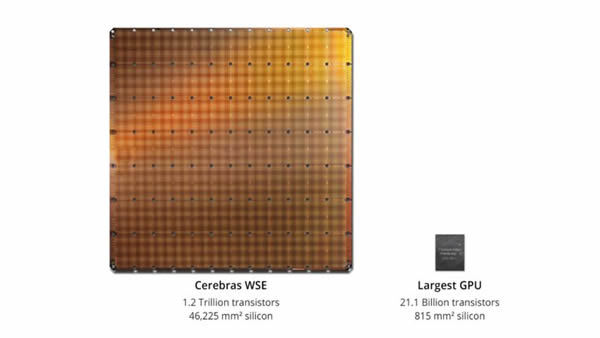

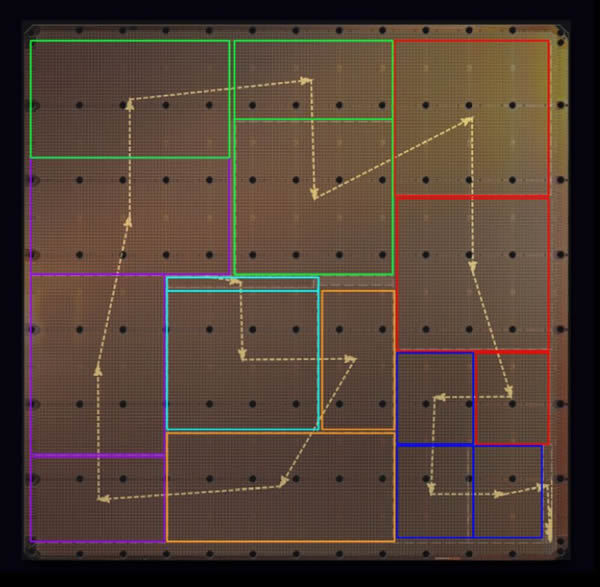

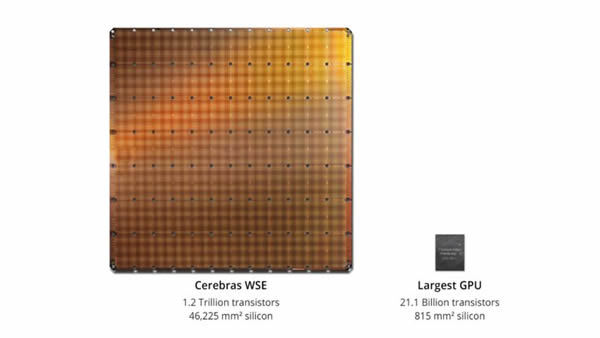

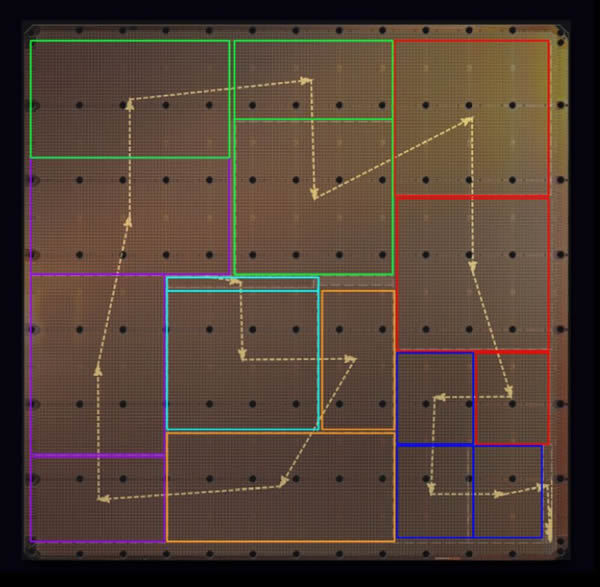

まず第一に、CS-1を特異なものにしているのはもちろんその心臓部、つまり30cm(12inch)ウェハーをまるごと使ったCPU(写真1)です。CerebrasはこれをWSE - Wafer Scale Engineと呼んでいます。そのサイズは215mm×215mm。ここに専用のプロセッサが40万コア含まれており、全体のトランジスタ数は1.2兆にも達します。プロセスはTSMCの16nmです。

写真1 30cm(12inch)ウェハーをまるごと使ったCPU

引用:Blog 1より。

引用:Blog 1より。

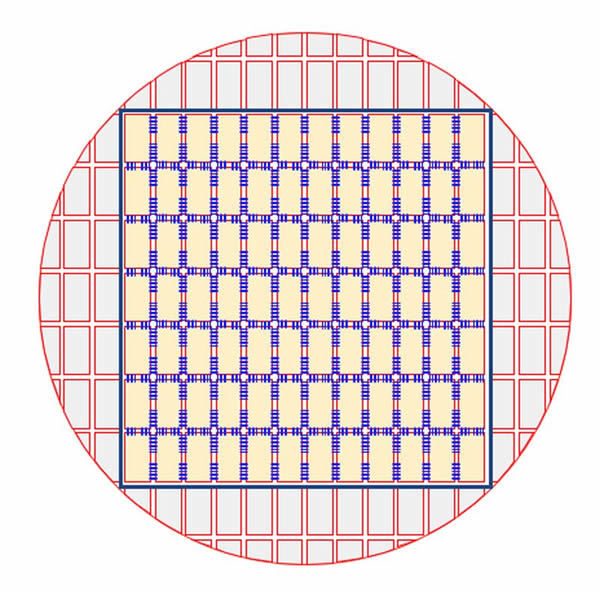

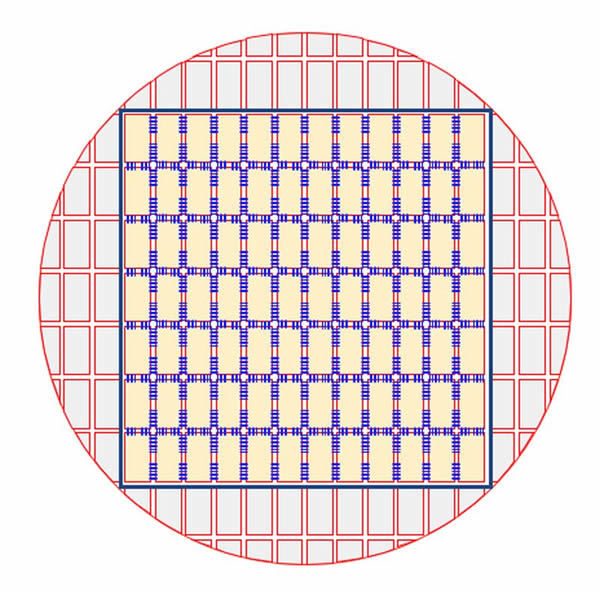

もともとウェハーは円形ですが、写真2に示したように周辺部分を切り落としてこの形にしています。通常のCPUなどでは、ウェハーの中の小さな長方形1つずつのサイズに切り分けて、それぞれが1つのチップの中に収まります。WSEは12×7つまり84チップを合わせて1つにしたようなものです。

写真2 ウェハーの切り落とし方

引用:Blog 1より。

引用:Blog 1より。

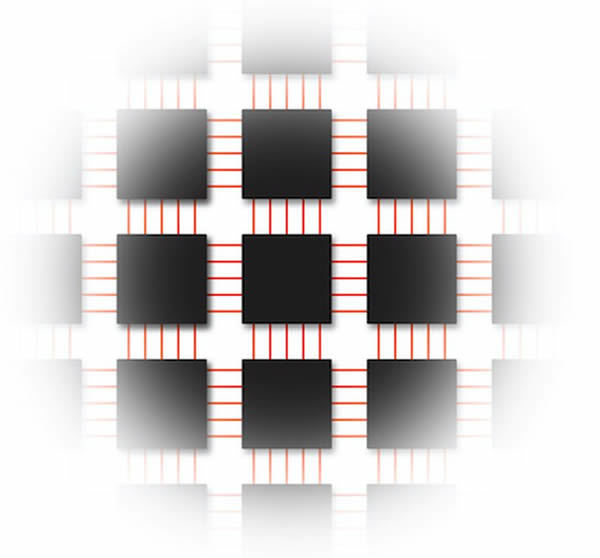

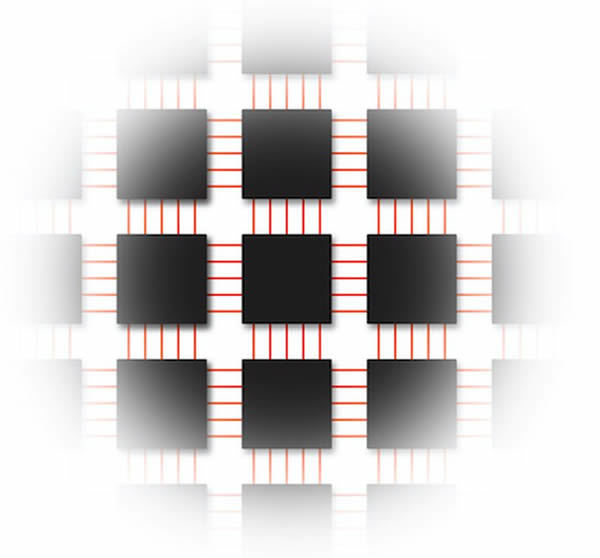

各チップ内部のコアは写真3のような2次元メッシュ構造のネットワークによって相互接続されています。そして、チップ間も前述の写真2の青い線、つまりチップ間の隙間を乗り越えた配線層を通じてつながれており、結果的にWSE全体で巨大な2次元メッシュネットワークを構成しています。WSEはこの四角に切り落とした左右の側面からデータの入出力が行われます。

写真3 各チップ内部のコアの構造

引用:Blog 2より。

引用:Blog 2より。

ところで通常、各チップは切り離して利用されます。そのため、このチップ間の隙間「スクライブ・ライン」上に金属による配線層を形成させることもありません、というかそんなことはできないように半導体の製造工程はできあがっています。つまりこれは製造工程そのものに手を入れる、半導体製造企業(今回はTSMC社)側の技術開発を必要とする、結構大変なアプローチです。

コアとメモリの配置

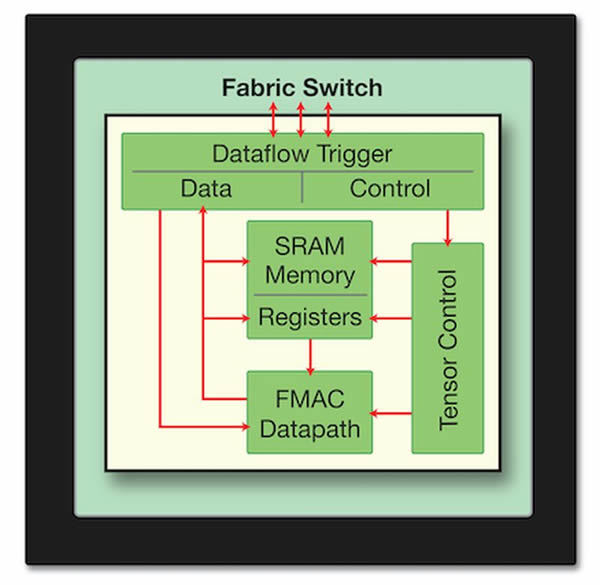

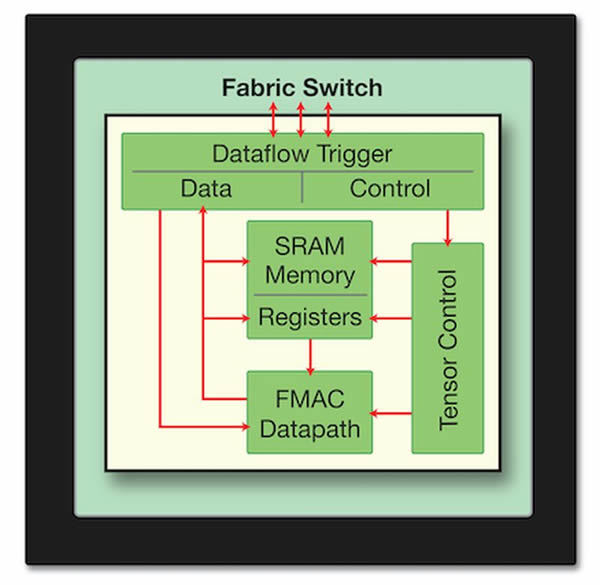

各プロセッサコアは独自設計、それも「データフロー」と呼ばれるアーキテクチャに基づいたものです。データフローとは、端的には「データが揃ったらそこでの計算が発火し、次の計算処理に対してデータ(結果)を送る」といったアイデアです。ニューラルネットワークのノード群による連鎖的な計算処理と親和性が高いことが想像できるでしょうか。

最近、つまりTensorFlowがこれを採用したため若い人たちには新しいものと映るかもしれませんが、1960年代からあるデータ処理モデルです。

写真4にコアの概略図があります。メモリが各コア内にあることがわかると思います。DRAMより遥かに高速(1クロックとのこと)に読み書きできるSRAM技術によるもので、WSE全体で18Gバイトもの容量になります。図中にFabric Switchとあるのが、コアを相互接続する二次元メッシュ・ネットワークとの接続部分です。

写真4 コア概略図

引用:Blog 2より。

引用:Blog 2より。

つまり広大な2次元メッシュ上に配置された大量のコアを使って、多層ニューラルネットワークの各層を写真5のように割り付けてデータを次々と流していく、というアーキテクチャなのです。

写真5 各層のニューラルネットワークをこのように割り付け、データを流す

引用:Blog 3より。

引用:Blog 3より。

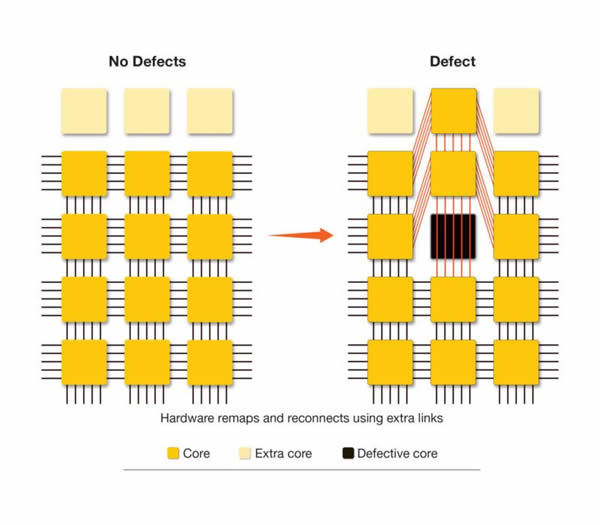

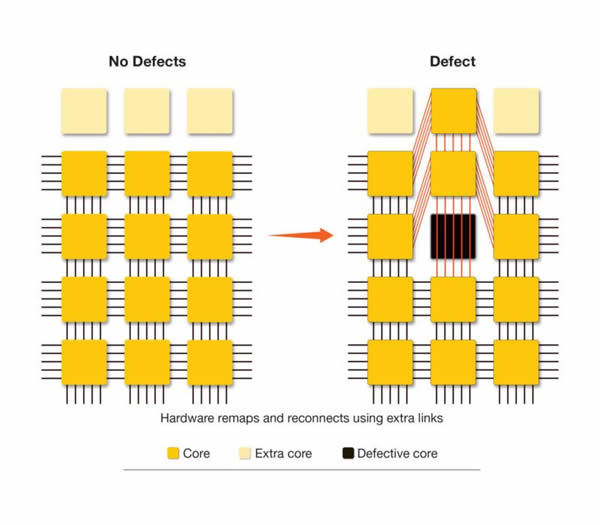

ところで半導体製造にはDefect、つまり回路形成の部分的な失敗が付きものです。通常は1枚のウェハーから多数のチップが切り出されますから、Defectのために不良となったチップは捨てることで対応することが可能です。

しかし、WSEはウェハー1つで単体の完成品ですから、たった1つの不良でウェハー丸ごと捨てるようなことはできません。結局、彼らは各チップ内に余剰のコアを用意しておき、Defectによって不良となったコアを「迂回する」ための配線をあらかじめ埋め込むことでこの問題に対応しました(写真6)。

写真6 余剰コアを用意し、不良時に対応できる

引用:Blog 1より。

引用:Blog 1より。

パッケージング

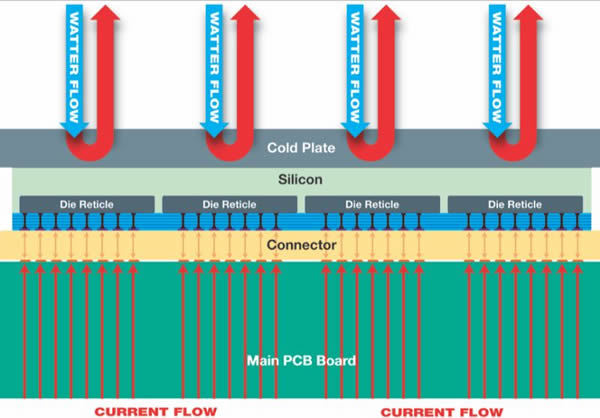

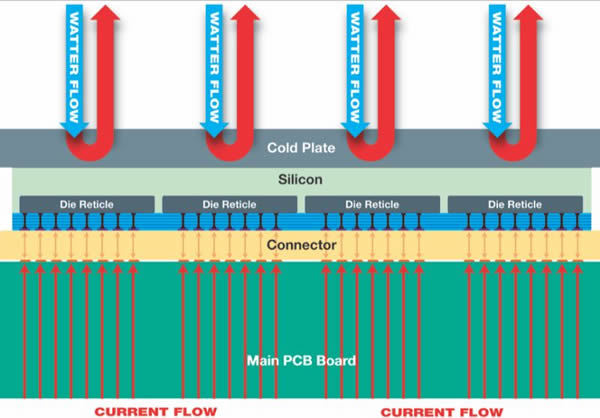

これだけ大きいと消費電力も大きく、15KWを越えます。写真7にあるように、電流はそのシリコンの表側から大量のピンを経由して供給します。そしてそこで発生する熱を、今度はその裏側にCold Plateを押し当て、そこに冷却液を流すことで冷やします。

写真7 電力の供給と排熱のための水の流れ

引用:Blog 1より。

引用:Blog 1より。

もちろんこれだけ熱が出て、かつサイズが大きいとシリコンとPCB(プリント基板)の熱膨張率の違いなども問題になります。Blog 1ではそこで重要な役割を果たす写真7中のConnector部分の材料を開発したとあります。

15KWをチップ数で割ると1つ200W以下ですから、大型チップとしてはそんなものかなと思う程度の面積あたりの熱発生量です。しかし低電圧(0.9V)・大電流をこの面積に集中させるのはかなり大変です。

他にもデータ入出力能力を高めるために100G Ethernetを12ポートも用意し、FPGAで直接これを受けてWSEに供給するなど、11月のSC19での発表資料『A successful week for Cerebras at Supercomputing 2019』を読んでいると、開発では次から次へと現れる各種の新しい課題を、さまざまな技術を組み合わせた総力戦でクリアした印象です。

さぞ毎日楽しい現場だったろうな!と想像します。

どのくらいクレイジーか、を書きたい

さてもう良いでしょう!

このまったく新しいマシンを生んだCerebras社の、スタートアップストーリーに進みましょう。

筆者はこの記事のために2019年12月にCerebras社を訪ねて取材を行いました。対応してくれたのはco-founderでありCTOであるGary Lauterbach氏と、Director of ProductであるAndy Hock氏です。

Cerebras、co-founderでありCTOであるGary Lauterbach氏(左)とDirector of ProductであるAndy Hock氏(右)

Cerebrasオフィス外観

Cerebrasオフィス外観

筆者がGaryと初めて会ったのは2013年、前職であるSeamicro/AMD時代です。それ以来継続的に会っており、過去にはCerebrasの源流とも言える、彼が手がけたいくつかのアーキテクチャに関する記事を出したりもしています[2]。そうした経緯もあり、取材は過去の我々の議論を踏まえたうえでの、雑談的な雰囲気で行われました。

筆者:今日はCerebrasのことについて、ただしその技術ではなく、スタートアップのストーリーに焦点を当てた取材のために来ました。

私は'80年代、'90年代のアーキテクチャ面での数々のイノベーションを見た世代ですが、ここしばらく革命的な挑戦はとても少なくなったと感じています。その中でCerebrasは強烈にクレイジーな挑戦をして、それを成し遂げました。だから私はCerebrasがどのくらいクレイジーかを書きたいのです(一同笑い)。

Andy:クレイジー、という意味では我々は……(Garyに向かって)ほぼトップ(頂点)に近いかな?

Gary:まあそうだね!(笑)多くの人たちが「この十年で最もクレイジー」と言ってくれたね。

最初のミーティングから資金を得るまで

まず、ウェハースケールのアイデア、つまりウェハーのまま、直接ダイどうしを接続するアイデアがどうやって生まれ、現実になったのかを聞きました。

筆者:あなたが過去に開発したDARPA HPCSについて2014年に議論したことを覚えています[3]。あれも1つのウェハーサイズ コンピュータですよね?

Gary:そうだね。確かにHPCSもCerebrasをやる動機の一部分だった。

筆者:その道のりを聞きたいです。この、ウェハーのままダイ間接続をするアイデアをいつ思いついたのですか?

Gary:4年半ほど前、Cerebrasのファウンダー達で集まって、自分たちがそれぞれにやってきた技術について議論したんだ。我々が会社としてできるかもしれない技術アイデアについて、それこそ3D XPoint メモリ、ソフトウェア、エミュレータなど広いレンジで検討した。それで議論が機械学習、ニューラルネットワークのことになったとき、そこに良いチャンスがあることがわかった。

つまりこのチーム、つまり私自身、Sean Lie、Michael James、Andrew(Feldman)、JP(Fricker) が[4]、この領域に良くマッチするスキルを持っている、とね。そこで我々はVCに話をし始めたんだ。

Andrew(現CEO)はビジネスマンだから技術の議論には関わらなかったが、他は毎週2回、Palo Alto図書館に集まって製品のコンセプトを作り上げていった。ニューラルネットワーク世界で最大勢力であるnVIDIAとどうやって競争するか、と。結局、我々がSun Lab.でやったproximity I/O技術の、シリコン上での莫大な帯域の確保がこの領域にとてもよく合うと結論を出した。

我々が十分なアイデアを得たところでAndrewが加わり、資金調達のためにそれらを1つに集めたスライドを作った。でも、私はAndrewに警告したんだ。これはとてつもなくリスキーだと。

“失敗したら大地に 30 年分の毒を撒いてしまうほどの影響がある。もし我々がVCたちに『我々はウェハースケールのコンピュータを作る』と言ったら、彼らは我々を部屋から追い出すだろうよ”。

しかし驚いたことに、このときAndrewは(どん、と机を叩いて)「やるんだよ!(Let's do it!)」と言ったんだ。

そうしてGreylock Partnersの会議室に行き、我々は大きな、つまりnVIDIAよりはるかに大きな帯域を取るためにウェハースケールのデバイスを作ろうとしていること、完成すればそれは業界が眼を見張るようなものになることなどを話した。

とてもリスキーだったが、そうして彼らはそのリスクにサインした。ただシリーズAのために私が作ったスライドでは、そこ(リスク)についてはあまりハイライトされてなかった(強調されてなかった)んだがね。私の記憶では。

筆者:いくつのVCが集まったのですか?

Gary:3つ。Eclipse Ventures、Foundation Capital、Benchmark Capitalだね。

筆者:彼らは皆リスクを取るのをOKだと言ったのですか?

Gary:(ここで3秒ほど沈黙)

筆者:えっ? NOなの?

Gary:私の記憶では、ウェハースケール技術のリスクについてはハイライトしてなかったね。我々はニューラルネットワークのアクセラレータを作る、と言ったんだ。GPUに対して桁違いのパフォーマンスを持った……

筆者:(割り込んで)ウェハースケールのコンピュータを作るって言わなかったの?

Gary:あまり話さなかったね(皆爆笑)。

Andy:補足すると、あのステージではどうやってウェハースケールを作るのか、いくつかのアプローチがあり得てまだ決まってなかったのです。

Gary:そう。どうやって作るかはまだ十分には検討されてなかったね(なるほど)。

Andy:もう1つ、ここ(シリコン)バレーには、ちょっと特別な投資家がいるのです。大志がある、特別にクレイジーなハードウェアプロジェクトに対して出資するのに、あまり資金の量や、プロジェクトのタイムライン(時間的計画)の説明を厳しく求めず、またリスクなどの完全な理解がなくても問題としない、といった人たちです。

たとえば、私の最後のプロジェクトは宇宙に送り出す衛星を作ることでしたが、これは作るのにとても長い時間がかかるし、リスクも高い。そうしたものにも出資者がいるんです。

Gary:Pierre Lamondはそうした種類の投資家だったね。彼はハードウェアの経験が豊富で、時間と資金が掛かることを理解して、ステップアップしていく間、長期の出資をしてくれた。

それから、今は9つほどの(主要な)投資家がいるが、それ以外にも個人投資家が含まれている。シリコンバレーの友達やその家族だったり、それ以外に20人ほどの個人がいるんだよ。すごく少額のね。

筆者:夢を買うって感じでしょうか?

Gary:動機はさまざまだね。最初の時期に、それも驚異的な(amazing=あきれるほど、の意もある)プロジェクトに出資してくれる個人だからね。我々のほうから彼らを招いたりして、技術やビジネスのアドバイザーを頼んだりすることもある。彼らに導いてもらいたいからね。

CerebrasのWebには有名なVCが名を連ねていますが、その下にそうした個人投資家の名前が並んでいます。Andy Bechtolsheim氏の名前もありますが、筆者としてはSDN(Software Defined Network)の創始者でもあるNick McKeown氏がいるのが気になります。

4年半

筆者:それにしても4年半で出せたとは、かなり速い開発ですね。

Gary:我々がやったことにしてみれば驚くべき短かさだね。数多くの技術を作り上げた。ウェハー・スケールだけじゃなく、パッケージング、冷却、電力供給、ソフトウェア。最後の段階に到達するまでに、とても多くの技術について取り組んだね。

筆者:いやあ、超速い(super fast)ですよ!

Gary:ああ。ただ出資者にはそう速くは見えなかったろうなと思うよ。(ははは)

ウェハースケールを実現するためのダイ間接続、つまりウェハー上でスクライブライン(ダイとダイの間の、通常ならそこで切断する領域)を越えるメタル層を作る作業が必要ですが、これはTSMCが行っています。GaryによればTSMCが初めてスクライブラインを越えた時の試作品の断面を電子顕微鏡で見たが、その段階でほとんどパーフェクトだったとのことです。ただ、GaryはこのTSMCの作業だけでなく、他の多くのパートもまた時間を要し、それらを組み上げて製品まで辿り着いたことを強調しました。

そして、これからはより優れたソフトウェアを積み上げていくことに多くの時間が必要になります。現時点で既にCS-1はTensorFlowやPyTorchなどに対応していますが、これからソフトウェアの厚みが増すと、それだけCS-1は強くなります。

「来年(2020年)はソフトウェアの年ですね」と聞くと、「もうソフトウェア・エンジニアが大部分になっている」とのことです。すでに全体で200人を越えたそうで、筆者が見ていた2年の間にしてもすごく速く成長していると思います。

取材中の様子。非常にアツい思いが伝わってきました

新しいパラダイムを作る

筆者:何年も掛けたCS-1の開発において、どこが一番おもしろいところでしたか?

Gary:これはグランドビジョン、つまりまったく新しいコンピュータシステムのパラダイムを作るものだった。つまり私は30年間、トラディショナルなプロセッサ設計の仕事をしてきた。そして君が指摘したとおり、プロセッサアーキテクチャはもうおもしろくなくなってしまったんだ。

もし私が新しいアーキテクチャの絵を描いて、そこで2%の性能改善があれば、それが大きな価値なんだ。でもCerebrasでは、10倍、100倍、1,000倍速くなるもののために働ける。まるっきり新しい仕事・データで、新しいアイデアを試すことができる。あるいは古いアイデアを新しい目的のために使う。これ(CS-1)は「大きく、新しいアイデアを試す」ことが自由にできる場所(sandbox)なんだ。

古いアイデアを新しくやり直す、というとGoogleがTPUで用いたシストリックアレイ構造もまた、'80年代の技術でした。Cerebrasも同様に2次元メッシュネットワークで大量のコアを相互接続していますが、シストリックアレイではなくデータフローのシステムです。

つまりシストリックアレイではデータは同期的にコア間を受け渡されますが、Cerebrasは非同期のメッセージングで結ばれています。そしてデータフローもまた、'70年代によく研究されたアイデアです。

Cerebrasオフィスエントランス脇にはWSEをかたどったデコレーションが

Gary:我々はここ何十年かの間に蓄積された、たくさんの技術的なアイデアを使ってるんだ。そしてこれをニューラルネットワークの仕事(ワークロード)に使う機会がひょっこり現れたわけだ。つまりこれまでマッシブな(並列度と処理量が極めて高い)データフロー処理はどうしても実現できなかった。

Arvind(Mithal)とJack Dennis[5]は何十年もMITで研究に取り組んだが、それでもデータフローマシンが使える領域はかなり限られていた。我々はオリジナルのコンセプトをそのまま、しかし40万プロセッサエレメント(PE)でやってみたわけだ。

筆者:過去の研究などではPEが少なすぎて、常にキューが溢れている(演算器が足りない)というのが結論だったと思います。

Gary:(そもそも)通常のシーケンシャルなプログラムをデータフローでやるのはほとんど不可能だ。しかし素晴らしいことに、我々のようなAI応用では、そもそもシーケンシャルなプログラムがないんだ。ニューラルネットワークは本来マッシブ・パラレルだから、プログラマがマッシブ・パラレルのプログラムやアルゴリズムを簡単に作れるようになる。

筆者:シストリックアレイ(TPU)、そしてデータフロー、ニューラルネットワーク。どれも私が80年代に良く見たものでした。これらがいま一つのところ、それもマッシブ・パラレルなところに集まっていて、それがとても興味深いです。

Gary:皆が1つのところに辿り着くのに 30年かかったんだね!

'80年代、第5世代コンピュータのころなど、Prologなどプログラミング言語はマッシブ・パラレルなプログラミングをするよう働きかけたが、しかしどれも結実することはなかった。人々は並列度の高いプログラムをうまく作る方法を突き止めることができなかった。しかしニューラルネットワークはそれをほとんどタダで我々にくれたんだ。まあ実際のところは逆で、我々は'80年代技術を集めて、そうしたアーキテクチャにマッチするワークロードを(Palo Alto図書館での議論で)捜したんだがね。

その結果、我々は「パーフェクト ストーム」を得た[6]わけだ。つまり「適切なワークロード、適切なアーキテクチャ、適切なテクノロジ」だね。

ただ加速するだけでなく

最後に話したのは、この広大なスペース、つまり大量のコンピューティング資源を何にどう使うか、ということです。

もちろんCS-1はディープラーニングのための大規模ニューラルネットワーク処理を高速化するために設計されたものですが、しかしこのようなアーキテクチャのシステムは今までに存在しなかったのです。つまり「既に存在している何かを加速する」だけでなく、「新しい何かを実現する」使い方もあり得るのでは無いかと考えるわけです。

筆者:顧客はこの大きなスペースをどう使うかを学ばないといけないのではないですかね。

Andy:我々はCS-1を(今存在するニューラルネットワークの仕事に)すぐに使えるようにするためにTensorFlowなど従来的なソフトウェアがそのまま移植できるようにしました。つまり新しいシステムですが、今までのプログラミングシステムがそのまま使えます。

しかし一方で、我々はこのシステムを今あるものを加速するためだけに作ったわけではありません。ニューラルネットワークの世界全体(Universe)を考えた時、我々はまだそのほんの一部しか発見(discover)していないのです。この世界の残りの領域にあるアプリケーションを顧客が見つけ出していくのには時間が掛かるでしょう。だからこそ我々は、我々がこれから見るもの、彼らがこのマシンでこれから作るものについてとてもワクワクしています。

Gary:我々はすでに、CS-1にうまくマップできるものでニューラルネットワークではない特定のワークロードを見つけてるよ。

筆者:今のディープラーニングの盛り上がりは、Googleなどが大規模なコンピューティング資源を持っていたから出てきたアプローチでした。もし、もっと大きなリソースを持ったら、また違うアプローチが出て来る可能性があるのだと思います。つまりこのCS-1は、そうした新しいリサーチワークの出発点となる、新しいプラットフォームになるかもしれません。

Andy、Gary:イエス。

Andy:すでに研究所や大学など、いくつかのユーザの手元にCS-1が投入されています。もう我々は新しい発見のすぐ隣にいます。日本のマーケットからの特定分野の要求も強くあります。産業界からも、大学からも。

筆者:あなた方の名前が「Cerebras前、Cerebras後」と呼ばれるような、マイルストーンとなることを望んでいます(笑)。

1階のラボで稼働していたCS-1の実機

おわりに

取材は1時間半ほどでしたが、そこで筆者は典型的なシリコバレーのスタートアップの物語を聞くことができました。地域の図書館にシード(種)となる技術を持っている旧知のエンジニアたちが集まり、突っ込むべき場面を定め、資金を募る。そこに集まっていたのは「何にせよ初めて」な若者ではなく既に多くの実績を積み上げた歴戦のチームです。

辿り着いたのは、そのチームなら必然ともいうべき壮大なアイデアでした。ニューラル・ネットワークの各プレーンを、シリコンウェハー全面を使った40万コア上に配置して全コアをデータフローで並列処理させる。そう言えば簡単に聞こえるかもしれませんが、レイヤの異なる多様な要素技術を組み上げて結合するのは容易なことではありません。

たとえば、CS-1では大量のデータ入出力を12本の100G Ethernetを通したTCP/IPコネクションで行いますが、これをよどみなく40万コアに流し込み続けるのは大変なことです。彼らの解決策はネットワークインターフェースをFPGAで直接構築し、TCP/IP処理をその中で終端して、直接ウェハーのエッジにデータを届ける、というアプローチです。もうこれだけで1つのスタートアップができてしまいそうですね!

そうした数多くの挑戦を積み上げて、最初の議論からわずか4年半で製品として世の中に出したことには驚嘆します。最初に握り締めたピュアな、しかし無謀とも言えるアイデアにひるまず、信じてやり抜いたCerebrasのチームに拍手を贈ります。

筆者はまた、2D Meshのマッシブ・パラレル コンピューティング、シストリックアレイ(GoogleのTPU)、そしてデータフローなど、自分自身が'80年代に多く見た当時の「新しい」コンピューティングモデルがいま結実しつつあることにある種の感慨を覚えます。Garyの言う「30年経って、皆が1つのところに辿り着いたんだ」とは、実に正しい説明だと感じます。

ストレートな議論から生まれた壮大なアイデアと、レイヤの異なる技術を集めた総力戦の物語。短い時間で多くのことに思考を巡らせた、楽しい取材となりました。

別れ際、Garyにもし次に何かやるならどんなもの?と聞いたら「もっとクレイジー(crazier)なのがいいね!」と答えてくれました。世界はエンジニアが回しているんだ、という誇りを感じる笑顔でした。